# GC4116

# MULTI-STANDARD QUAD DUC CHIP

# **DATA SHEET**

This datasheet may be changed without notice.

Texas Instruments reserves the right to make changes in circuit design and/or specifications at any time without notice. The user is cautioned to verify that datasheets are current before placing orders. Information provided by Texas Instruments is believed to be accurate and reliable. No responsibility is assumed by Texas Instruments for its use, nor for any infringement of patents or other rights of third parties which may arise from its use. No license is granted by implication or otherwise under any patent rights of Texas Instruments.

# **REVISION HISTORY**

| Revision | Date             | Description                                                                                                                                                                           |

|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1      | February 8, 2000 | Original                                                                                                                                                                              |

| 0.2      | March 22, 2000   | Corrected typos, and miscellaneous errors.                                                                                                                                            |

| 0.3      | October 31, 2000 | Rewritten throughout to reflect new modes, final design changes                                                                                                                       |

| SLWS135  | April 27, 2001   | Modified to reflect Production specifications. Changes throughout.                                                                                                                    |

| SLWS135A | May 15, 2002     | Modified to reflect 106 MHz clock<br>New UMTS transmit filter response,<br>Sum I/O gain equation corrected,<br>Section 7.0 application notes completed.<br>Clarifications throughout. |

| 1.0        |                          | KEY FEATURES                                                                                                | . 1        |

|------------|--------------------------|-------------------------------------------------------------------------------------------------------------|------------|

| 2.0        |                          | BLOCK DIAGRAM                                                                                               | . 1        |

| 3.0        |                          | FUNCTIONAL DESCRIPTION                                                                                      | . 2        |

|            | 3.1<br>3.2<br>3.3<br>3.4 | CONTROL INTERFACE<br>CHANNEL INPUT FORMAT<br>THE UP-CONVERTERS<br>THE OVERALL INTERPOLATION FILTER RESPONSE | . 4<br>. 5 |

|            | 3.5                      | THE SUM TREE                                                                                                |            |

|            | 3.6                      | OVERALL GAIN                                                                                                |            |

|            | 3.7                      | FOUR CHANNEL RESAMPLER                                                                                      |            |

|            | 3.8<br>3.9               | SERIAL CONTROLLER                                                                                           |            |

|            | 3.10                     | POWER DOWN MODES                                                                                            |            |

|            | 3.11                     | SYNCHRONIZATION                                                                                             |            |

|            | 3.12                     | INITIALIZATION                                                                                              |            |

|            | 3.13                     | DATA LATENCY                                                                                                |            |

|            | 3.14                     | DIAGNOSTICS                                                                                                 |            |

|            | 3.15                     |                                                                                                             |            |

| 4.0        | 3.16                     | MASK REVISION REGISTER                                                                                      |            |

| 4.0<br>5.0 |                          | CONTROL REGISTERS                                                                                           |            |

| 5.0        | 5.1                      | GLOBAL REGISTERS                                                                                            |            |

|            | 5.2                      | PAGED REGISTERS                                                                                             |            |

|            | 5.3                      | FREQUENCY AND PHASE PAGES (PAGES 0 AND 1)                                                                   |            |

|            | 5.4                      | INPUT GAIN PAGE (PAGE 2)                                                                                    |            |

|            | 5.5                      | CHANNEL INPUT PAGE (PAGE 3)                                                                                 |            |

|            | 5.6                      | RESAMPLER INPUT PAGE (PAGE 4)                                                                               |            |

|            | 5.7                      | I/O CONTROL PAGE (PAGE 7)                                                                                   |            |

|            | 5.8<br>5.9               | RESAMPLER CONTROL PAGE (PAGE 8)<br>RESAMPLER RATIO PAGE (PAGE 9)                                            |            |

|            | 5.10                     | PFIR COEFFICIENT PAGES (PAGES 16 to 31)                                                                     |            |

|            | 5.11                     | RESAMPLER COEFFICIENT PAGES (PAGES 32-63)                                                                   |            |

| 6.0        |                          | SPECIFICATIONS                                                                                              | 43         |

|            | 6.1                      | ABSOLUTE MAXIMUM RATINGS                                                                                    |            |

|            | 6.2                      | RECOMMENDED OPERATING CONDITIONS                                                                            |            |

|            | 6.3                      | THERMAL CHARACTERISTICS                                                                                     | -          |

|            | 6.4                      | DC CHARACTERISTICS                                                                                          |            |

|            | 6.5                      | AC CHARACTERISTICS                                                                                          | .0         |

| 7.0        |                          | APPLICATION NOTES                                                                                           |            |

|            | 7.1<br>7.2               | POWER AND GROUND CONNECTIONS                                                                                |            |

|            | 7.2<br>7.3               | MOISTURE SENSITIVE PACKAGE                                                                                  |            |

|            | 7.4                      |                                                                                                             |            |

|            | 7.5                      | REFERENCE DESIGNS                                                                                           |            |

|            | 7.6                      | EXAMPLE PFIR FILTER SETS                                                                                    |            |

|            | 7.7                      | EXAMPLE RESAMPLER CONFIGURATIONS                                                                            |            |

|            | 7.8                      | NOISE ANALYSIS                                                                                              |            |

|            | 7.9<br>7.10              | EXAMPLE GSM APPLICATION<br>EXAMPLE IS-136 DAMPS APPLICATION                                                 |            |

|            | 7.10                     | EXAMPLE IS-136 DAMPS APPLICATION<br>EXAMPLE IS-95 NB-CDMA (CDMA2000-1X) APPLICATION                         |            |

|            | 7.12                     | EXAMPLE UMTS WB-CDMA (CDMA2000-TX) AT LICATION                                                              |            |

|            | 7.13                     | DIAGNOSTICS                                                                                                 |            |

|            | 7.14                     | OUTPUT TEST CONFIGURATION                                                                                   |            |

|            | 7.15                     | INPUT TEST CONFIGURATION                                                                                    | 49         |

# LIST OF FIGURES

| Figure 1:  | GC4116 Block Diagram1                            |

|------------|--------------------------------------------------|

| Figure 2:  | Normal Control I/O Timing                        |

| Figure 3:  | Edge Write Control Timing3                       |

| Figure 4:  | Serial Input Formats4                            |

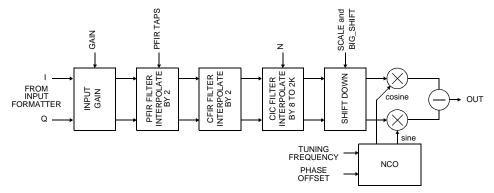

| Figure 5:  | The Up-converter Channel5                        |

| Figure 6:  | The Up-converter Channel                         |

| Figure 7:  | Five Stage CIC Interpolate by N Filter7          |

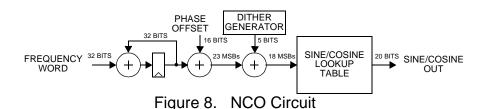

| Figure 8:  | NCO Circuit8                                     |

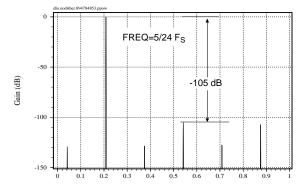

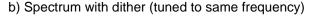

| Figure 9:  | Example NCO Spurs8                               |

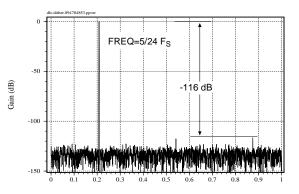

| Figure 10: | NCO Peak Spur Plot8                              |

| Figure 11: | Overall Filter Response                          |

| Figure 12: | Resampler Channel Block Diagram11                |

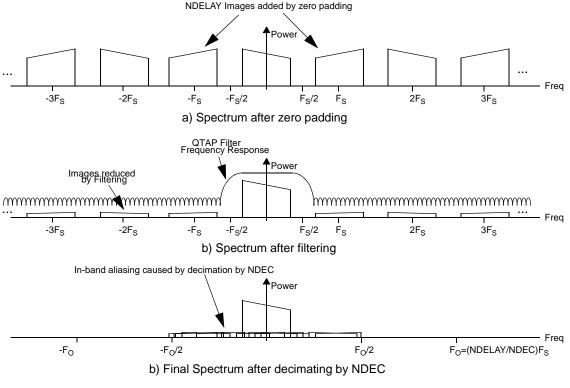

| Figure 13: | The Resampler's Spectral Response12              |

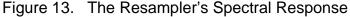

| Figure 14: | Resampler Serial Output14                        |

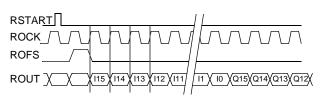

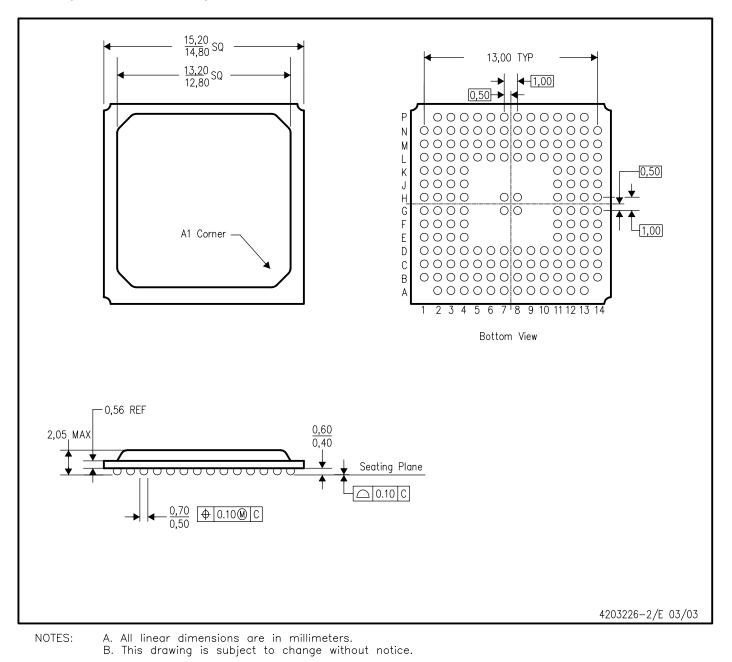

| Figure 15: | 160 Pin Plastic Ball Grid Array (PBGA) Package19 |

| Figure 16: | Reference Design Without the Resampler           |

| Figure 17: | Reference Design Using the Resampler             |

# LIST OF TABLES

| Table 1:  | Sync Modes                                       |    |

|-----------|--------------------------------------------------|----|

| Table 2:  | Sync Modes Sync Descriptions                     |    |

| Table 3:  | Mask Revisions                                   |    |

| Table 4:  | GC4116 Pin Out Locations Top View                | 20 |

| Table 5:  | GLOBAL CONTROL REGISTERS                         | 23 |

| Table 6:  | Page Assignments                                 |    |

| Table 7:  | IO Control Page Registers (Page 5)               |    |

| Table 8:  | Resampler Control Registers                      |    |

| Table 9:  | Resampler Ratio Page                             |    |

| Table 10: | PFIR Coefficient Pages                           |    |

| Table 11: | Resampler Coefficient Pages (Single filter mode) |    |

| Table 12: | Absolute Maximum Ratings                         |    |

| Table 13: | Recommended Operating Conditions                 |    |

| Table 14: | Thermal Data                                     |    |

| Table 15: | DC Operating Conditions                          |    |

| Table 16: | AC Characteristics                               |    |

# 1.0 KEY FEATURES

- Output rates up to 106 MSPS

- Four identical up-convert channels

- 16 bit real or complex inputs

- Four bit serial input ports, or memory mapped input registers

- Serial interface controller simplifies interfacing with ASICs or DSP chips

- Resampler circuit filters, pulse shapes and resamples data to allow arbitrary input to output sample rate conversion

- Interpolation factors of 32 to 5,792 in each channel 16 to 32 by combining two channels

- Independent frequency, phase and gain controls

- User programmable 63 tap input filter

- 0.02 Hz tuning resolution

- 115 dB Spur Free Dynamic Range

- 90 dB or more image rejection

- 0.07 dB gain resolution

- 0.05 dB peak to peak passband ripple

- The four channels are summed into a single output signal

- 22 bit sum I/O path to merge outputs from multiple GC4116 chips

- 8 to 22 bit 2's complement or offset binary output samples

- Accepts QPSK or QAM symbol data directly, performs transmit (pulse shape) filtering

- Performs pulse shaping and phase equalization for IS95 and CDMA2000

- Exceeds Damps, GSM, & IS95 requirements

- Supports up to two 4 Mbaud channels.

- Microprocessor interface for control

- Built in diagnostics

- Each GC4116 chip upconverts: Four GSM, DAMPS, or IS95 carriers, or Two 3X CDMA2000 carriers, or Two 3.84MB UMTS carriers

- Power consumption at 70 MHz, 2.5 volts: 84 mW per DAMPS channel 107 mW per GSM channel 305mW per 3.84MB UMTS channel

- Industrial temperature range (-40C to +85C)

- GC4116PB 160 ball PBGA (15mm by 15mm) package

- 3.3volt I/O voltage, 2.5volt core voltage

- JTAG Boundary Scan

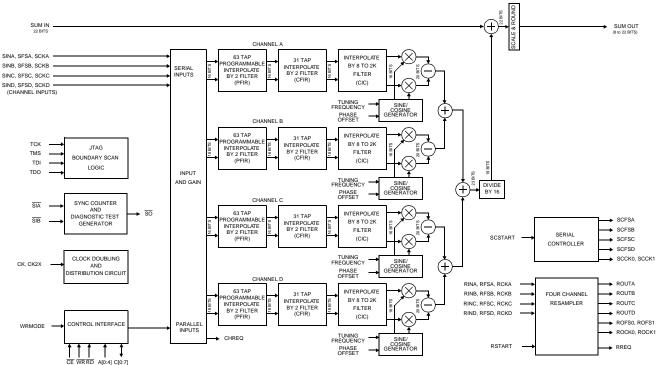

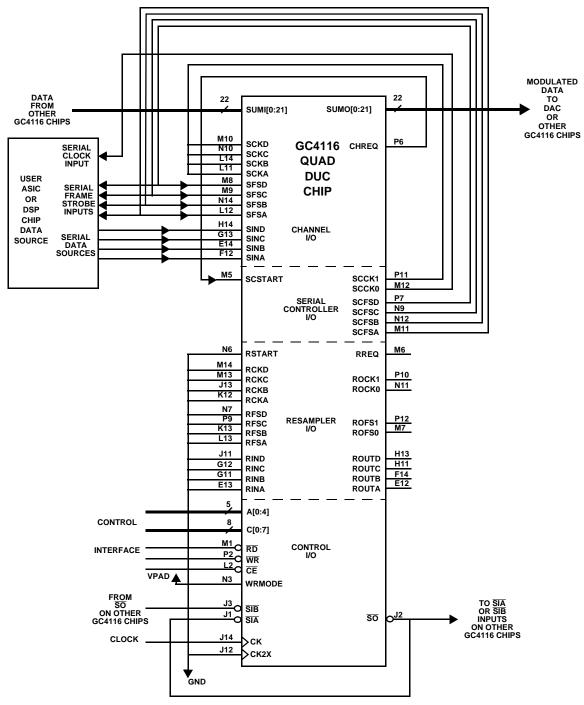

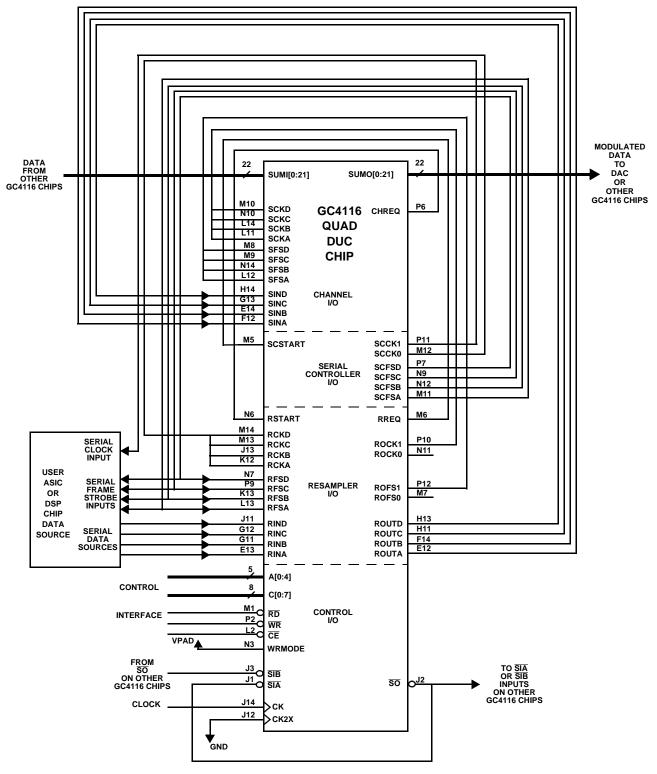

Figure 1. GC4116 Block Diagram

© 2002 Texas Instruments Incorporated - 1 -

#### This document contains information which may be changed at any time without notice

# 2.0 BLOCK DIAGRAM

# 3.0 FUNCTIONAL DESCRIPTION

The GC4116 quad transmit chip contains four identical up-conversion channels. The up-convert channels accept real or complex signals, interpolate them by programmable amounts ranging from 32 to 5,792, and modulates them up to selected center frequencies. The modulated signals are then summed together and optionally summed with modulated signals from other GC4116 chips. Channels can be used in pairs to reduce the interpolation ratio down to 16 in order to process wider band input signals.

Each channel contains a user programmable input filter (PFIR) which can be used to shape the transmitted signal's spectrum, or can be used as a Nyquist transmit filter for shaping digital data such as QPSK, GMSK or QAM symbols (See Section 7 for example applications).

The up-converter channels are designed to maintain over 115 dB of spur free dynamic range. Each up-convert channel accepts 16 bit inputs (bit serial) and produces 20 bit outputs. The up-converter outputs are summed with an external 22 bit input to produce a single 22 bit output. The chip can output either real or complex data. The frequencies and phase offsets of the four sine/cosine sequence generators can be independently specified, as can the gain of each circuit. Each channel interpolates by the same amount, but can be programmed with independent PFIR coefficients. Channels can be synchronized to support beamformed or frequency hopped systems.

An independent resampler block performs resampling on up to 4 signals. The resampler has its own input and output pins so that it can be used independently from the up-convert channels. The resampler engine is identical to the one in the gc4016. It provides a user programmable filter up to 512 taps long and allows for sampling by arbitrary amounts with delay resolutions up to 64 time phases.

A serial controller block is used to generate serial clocks and frame strobes for the channel and resampler input ports. This block simplifies interfacing the GC4116 to other devices.

On chip diagnostic circuits are provided to simplify system debug and maintenance.

The chip receives configuration and control information over a microprocessor compatible bus consisting of an 8 bit data I/O port, a 5 bit address port, a chip enable strobe, a read strobe and a write strobe. The chip's 110 control registers (8 bits each) and five coefficient RAM's are memory mapped into the 5 bit address space of the control port using an internal page register.

# 3.1 CONTROL INTERFACE

The chip is configured by writing control information into control registers within the chip. The control registers are grouped into 8 global registers and 64 pages of registers, each page containing up to 16 registers. The global registers are accessed as addresses 0 through 15. Address 15 is the page register which selects which page is accessed by addresses 16 through 31. The contents of these control registers and how to use them are described in Section 5.

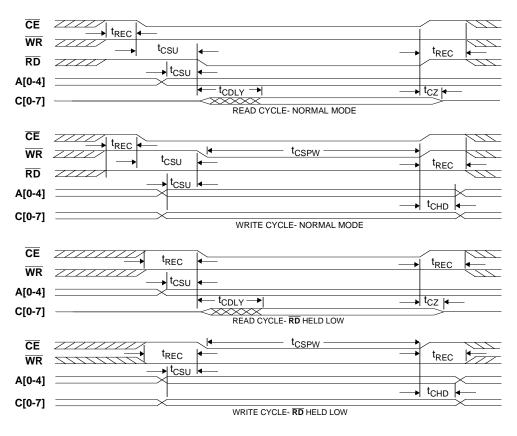

The registers are written to or read from using the C[0:7], A[0:4],  $\overline{CE}$ ,  $\overline{RD}$  and  $\overline{WR}$  pins. Each control register has been assigned a unique address within the chip. This interface is designed to allow the GC4116 chip to appear to an external processor as a memory mapped peripheral (the pin  $\overline{RD}$  is equivalent to a memory chip's  $\overline{OE}$  pin).

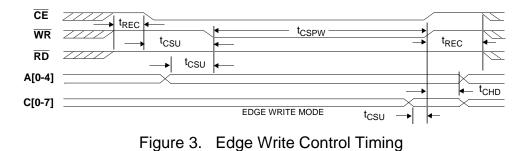

An external processor (a microprocessor, computer, or DSP chip) can write into a register by setting A[0:4] to the desired register address, selecting the chip using the  $\overline{CE}$  pin, setting C[0:7] to the desired value and then pulsing  $\overline{WR}$  low. The data will be written into the selected register when both  $\overline{WR}$  and  $\overline{CE}$  are low and will be held when either signal goes high. An alternate "edge write" mode can be used to strobe the data into the selected register when either  $\overline{WR}$  or  $\overline{CE}$  goes high. This is useful for processors that do not guarantee valid data when the write strobe goes active, but guarantee that the data will be stable for the required set up time before the write strobe goes inactive. The edge write is necessary for these processors, as some control registers (such as most sync registers) are sensitive to transient values on the C[0:7] data bus.

To read from a control register the processor must set A[0:4] to the desired address, select the chip with the  $\overline{CE}$  pin, and then set  $\overline{RD}$  low. The chip will then drive C[0:7] with the contents of the selected register. After the processor has read the value from C[0:7] it should set  $\overline{RD}$  and  $\overline{CE}$  high. The C[0:7] pins are turned off (high impedance) whenever  $\overline{CE}$  or  $\overline{RD}$  are high or when  $\overline{WR}$  is low. The chip will only drive these pins when both  $\overline{CE}$  and  $\overline{RD}$  are low and  $\overline{WR}$  is high.

One can also ground the  $\overline{RD}$  pin and use the  $\overline{WR}$  pin as a read/write direction control and use the  $\overline{CE}$  pin as a control I/O strobe. Figure 2 shows timing diagrams illustrating both I/O modes.

The edge write mode, enabled by the **WRMODE** input pin, allows for rising edge write cycles. In this mode the data on the **C[0:7]** pins only need to be stable for a small setup time before the rising edge of the write strobe, and held for a small hold time afterwards. This mode is appropriate for processors that do not provide stable data before the start of the write pulse. Figure 3 shows the timing for this mode. The setup, hold and pulse width requirements for control read or write operations are given in Section 6.0.

This document contains information which may be changed at any time without notice

#### SLWS135A - JUNE 2002

# 3.2 CHANNEL INPUT FORMAT

The input samples are 16 bits, either real or complex. The samples are input to the chip either through the bit-serial input ports, or through memory mapped control registers. The channel data request signal (CHREQ) is output from the chip to identify when the GC4116 is ready for another complex input sample or pair of real samples.

# 3.2.1 Bit Serial Interface

The bit serial format consists of a data input pin (SIN), a bit clock pin (SCK), and a frame strobe pin (SFS) for each of the four channels (A,B,C and D), and a channel data request pin (CHREQ) which is common to all channels.

The serial channel inputs can come directly from the Four Channel Resampler by connecting the resampler's serial output ports to the channel's serial input ports, and connecting the CHREQ pin to the resampler's RSTART pin. The Resampler and its I/O interface is described in Section 3.7.

If the Resampler is not being used, then the Serial Controller can be used to generate the proper serial clocks and frame strobes fro the channel inputs. In this case CHREQ is tied to SCSTART, and then SCCK and the SCFS strobes are used to drive the serial clock and frame strobes for both the channel inputs and the channel data source (typically a DSP chip, FPGA, or ASIC).

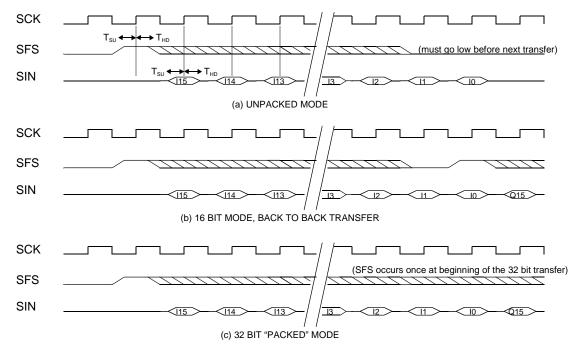

The bit serial samples are always entered MSB first. Complex values are entered I-half first followed by the Q-half. Real values are entered as pairs of samples, with the first sample in the I-half and the second sample in the Q-half. The input accepts either pairs of 16 bit words each with its own frame strobe (the unpacked mode), or as a single 32 bit transfer with a single frame strobe (the packed mode). The bit serial input formats are shown in Figure 4

Figure 4a shows the unpacked input mode (PACKED in the input control register is low). The user provides a bit serial clock (SCK), a frame strobe (SFS) and a data bit line (SIN). The chip clocks SFS and SIN into the chip on the rising edge of SCK (or falling edge if the SCK\_POL bit in the input control register is set). The user sends a 16 bit serial input word to the GC4116 by setting SFS high (or low if SFS\_POL in the input control register is set) for one SCK clock cycle, and then transmitting the data, MSB first, on the next 16 SCK clocks. The SFS may remain high during the transfer, but must go low for one SCK cycle before the next serial word is sent. The serial sample is transferred to a parallel register on the next SCK clock. Additional SCK clocks are acceptable but are ignored. The data can be transmitted "back to back" as shown in Figure 4b as long as the SFS signal toggles low and then high as shown. If the PACKED control bit is high, then the I and Q samples (or I0 then I1 for real data) are sent as a single 32 bit word with only one SFS strobe as shown in Figure 4c.:

Figure 4. Serial Input Formats

© 2002 Texas Instruments Incorporated

This document contains information which may be changed at any time without notice

- 4 -

The GC4116 input interface sends a channel data request strobe (CHREQ) when a new input sample is required for the up-converter channels. The CHREQ strobe is output from the chip every 4N clocks, where N is the interpolation ratio in the CIC filter. The pulse width of the CHREQ strobe is one CK period. The polarity of CHREQ is user programmable. The CHREQ strobe is typically connected to SCSTART of the serial request controller, or to RSTART of the resampler (See Section 3.7.9). CHREQ can also be used as an interrupt to an external device to tell it to send another input sample. The GC4116 chip must receive the last data bit at least three CK clocks before the next CHREQ strobe. See Section 3.11 for the timing relationship between SIA and CHREQ.

The frame sync can be sent up to 9 clock cycles (CK, not SCK) before CHREQ. This is normally used when the serial interface timing is tight, i.e., the CHREQ rate is less than 34 SCK cycles, so that there is not time between CHREQ strobes to send SFS, then 32 bits and then have at least 3 CK cycles before the next CHREQ.

Very Important Note: The chip requires that SCK be active when frame sync occurs, and be active for one cycle after the last bit is sent. Serial data can be sent using only 32 SCK clocks per CHREQ period if the frame sync for the 16 bit I word (or the 32 bit I/Q word in the PACKED mode) is coincident with the last bit of the previous transfer. The Serial Controller block described in Section 3.8 can provide appropriately timed frame strobes and serial clocks.

#### 3.2.2 Memory Mapped Interface

Input samples can be entered into the chip using the control interface. Addresses 16 through 31 on page 3 are the input data registers. Note that these registers can be written to in a DMA burst, 8 bits at a time. Note that some DMA formats write samples most significant byte first. If this is the case then the DMA should write from address 31 down to address 16. The CHREQ strobe from the GC4116 chip defines when the DMA transfer can start. The transfer must

be done before the next CHREQ strobe is received. See global address 14 for handshake details.

#### 3.3 THE UP-CONVERTERS

Each up-converter channel uses a two stage interpolate by four filter and a 5 stage cascaded integrate-comb (CIC) filter to increase the sample rate of the input data up to the chip's clock rate. An NCO and mixer circuit modulates the signal up to the desired center frequency.

A block diagram of each up-convert channel is shown in Figure 5. Each input sample is multiplied by an 8 bit 2's complement gain word. The gain adjustment is GAIN/128, where the gain word (GAIN) ranges from -128 to +127. This gives a 42 dB gain adjustment range. Setting G to zero clears the channel input. A different gain can be specified for each channel. The gain values are double buffered and may be transferred to the active register on a sync. The transfer is delayed so that the new values take effect on the same sample for all channels. Gain is described in more detail in Section 3.6.

After the gain has been applied, the input samples are interpolated by a factor of 2 in a 63 tap filter with programmable coefficients (PFIR). A typical use of the PFIR is to implement matched (root-raised-cosine) transmit filters.

The PFIR will also, if desired, convert real input data to single-sideband complex data. In this mode the PFIR does not interpolate by a factor of 2. Instead it down-converts the input data by  $F_S/4$ , where  $F_S$  is the input sample rate, and low pass filters the result.

The second interpolate by 2 filter is a 31 tap compensating filter (CFIR) which both interpolates by 2 and pre-compensates for the droop associated with the CIC filter that follows it.

The CIC filter interpolates by another factor of N=(8 to 1,448) to give an overall interpolation factor of 32 to 5,792 (16 to 2,896 in the real input mode).

© 2002 Texas Instruments Incorporated

- 5 -

This document contains information which may be changed at any time without notice

The interpolated signal is modulated by a sine/cosine sequence generated by the NCO. In the real output mode the real part (I-half) of the complex result is saved as the channel output.

In the complex output mode the CIC interpolation is cut in half and the NCO/mixer calculates both the I-half and Q-half of the complex result. In this mode the complex output sample rate is one-half the clock rate, with the I and Q halves multiplexed together onto the same output bus.

# 3.3.1 The Programmable Interpolate By 2 Filter (PFIR)

The input samples are filtered by two stages of interpolate by 2 filtering before they are interpolated by the CIC filter. The first stage interpolate by two filter is a 63 tap filter with programmable 16 bit coefficients. The PFIR will accept either complex or real input data. If the input samples are complex, the filter doubles the input rate by inserting zeroes between each sample, and then low pass filters the result. If the input samples are real (REAL in address 1 is set), the filter translates the real samples down by  $F_{IN}/4$ , where FIN is the input sample rate, by multiplying them by the complex sequence +1, -j, -1, +j, ..., and then lowpass filters the result. This generates a single-sideband modulation of the real input. Note that in the real input mode the data is entered as pairs of samples packed into the complex input word format (see Section 3.2). If double sideband real upconversion is desired, then the chip should be operated in the complex mode with the Q-half of each complex pair set to zero.

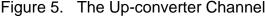

The PFIR filter passband must be flat in the region of the signal of interest, and have the desired out of band rejection in the region that will contain the interpolation image. Figure 6 illustrates the passband and stopband requirements of the filter.  $F_{IN}$  is the input sample rate to the channel.  $2F_{IN}$  is the output sample rate of the PFIR. A common use of the PFIR is to pulse shape digital data. The PFIR will accept QPSK, O-QPSK, PSK, PAM, OOK,  $\pi$ /4-QPSK, or QAM symbols and then filter them by the desired pulse shaping filter, which is commonIt a root-raised-cosine (RRC) filter. The symbols can be entered directly into the chip at the desired symbol (baud) rate. The application notes in Section 7 describes sample filter coefficients sets for common standards (DAMPS, GSM, IS95, UMTS).

Each channel has its own PFIR coefficient memory, so the same filter, or a different filter, can be used in each channel.

The user downloaded filter coefficients are 16 bit 2's complement numbers. Unity gain will be achieved through

Figure 6. Typical PFIR Specifications the filter if the sum of the 63 coefficients is equal to 65536. If the sum is not 65536, then PFIR will introduce a gain equal to:  $PFIR\_GAIN = \frac{PFIR\_SUM}{65536}$ , where PFIR\_SUM is the sum of the 63 coefficients.

The 63 coefficients are identified as coefficients  $h_0$  through  $h_{62}$ , where  $h_{31}$  is the center tap. The coefficients are assumed to be symmetric, so only the first 32 coefficients ( $h_0$  through  $h_{31}$ ) are loaded into the chip. A non-symmetric mode (NO\_SYM\_PFIR in address 26) allows the user to download a 32 tap non-symmetric filter as taps  $h_0$  through  $h_{31}$ . The newest sample is multiplied by h31 and the oldest is multiplied by  $h_{01}$ .

# 3.3.2 The Compensating Interpolate by 2 Filter (CFIR)

The second stage filter is a fixed coefficient 31 tap interpolate by 2 filter. The second stage filter always interpolates by a factor of two. The second filter has a passband which is flat (0.01 dB ripple) out to  $0.6F_{IN}$  and provides over 90dB of image rejection beyond  $1.4F_{IN}$ . The second filter also compensates for the droop associated with the CIC interpolation filter described in the next section. The 16 unique coefficients of the symmetric filter are:

-34, -171, -166, 403, 837, -317, -1983, -790, 2820, 3328, -1667, -6589, -4024, 7232, 20602, 26577

The passband of this filter is wide enough to upconvert digital symbol data with excess bandwidths up to 0.35.

The CFIR output is scaled to have unity gain.

The output rate of the CFIR filter is  $4F_{IN}$  in the complex input mode and is  $2F_{IN}$  in the real input mode. The CFIR output rate relative to the clock rate is  $F_{CK}/N$

```

© 2002 Texas Instruments Incorporated

```

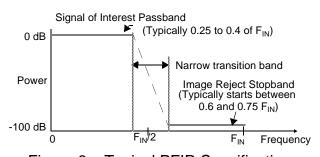

Figure 7. Five Stage CIC Interpolate by N Filter

#### 3.3.3 The CIC Interpolate by N Filter

The CFIR output is interpolated by a factor of N in the CIC<sup>1</sup> filter, where N is any integer between 8 and 1,448. The filter is a 5 stage CIC filter. A block diagram of the CIC filter is shown in Figure 7. The output of the CIC interpolation filter is equal to the clock rate. The CIC filter has a gain equal to N<sup>4</sup> which must be removed by the "SCALE AND ROUND" circuit shown in Figure 7. This circuit has a gain equal to 2<sup>-(3+SCALE+12\*BIG\_SHIFT)</sup>, where SCALE ranges from 0 to 15 and BIG\_SHIFT ranges from 0 to 2. The value chosen for BIG\_SHIFT must also satisfy:  $2^{(12*BIG_SHIFT+18)} \ge N^4$ . Overflows due to improper gain settings will go undetected if this relationship is violated. This restriction means that N must be less than 23 for BIG\_SHIFT = 0, N must be less than 182 for BIG\_SHIFT = 1, and N must be less than 1449 for BIG\_SHIFT = 2. Larger interpolation amounts can be achieved by using the resampler to perform interpolation. Larger interpolation amounts using the CIC can be accomplished only by reducing the signal amplitude feeding the CIC.

The CIC filter must be initialized when the chip is first configured or whenever the interpolation value N or the shift value BIG\_SHIFT are changed. The CIC filter is initialized using the flush controls described in Section 5.8. If the CIC is disturbed during processing due to noise, radiation particles, or due to changing N or BIG\_SHIFT, then the CIC will generate wideband white noise in the output. This property is inherent in the mathematics of a CIC filter used for interpolation. This instability can be prevented by using the chip<sup>2</sup> "auto flush" capability of the (See DISABLE AUTO FLUSH in control register 13). The auto flush mode detects CIC instability and automatically re-initializes the CIC. The auto flush mode requires that the gain up to the output of the CIC filter is less than or equal to unity.

#### 3.3.4 Wideband Input Mode

The overall interpolation factor of an up convert channel is 4N. The minimum value of N is 8, which limits the maximum input sample rate to be  $F_{CK}/32$ . If the clock rate is 100 MHz, then the maximum single channel input bandwidth is between 2 and 3 MHz. Wider input bandwidths can be handled by combining two channels into a single wideband channel using the SplitIQ mode (SPLITIQ in register 1). In the split IQ mode the complex input data is split between two channels. One channel up converts the I-half and the other channel up converts the Q-half. This allows the channels to process data at twice the rate so the minimum CIC interpolation is N=4 (rather than the previous N=8).

The input data is entered as two samples per CHREQ cycle. The I-half inputs are packed into complex words (I0 with I1, for example) and input into the first channel. The Q-half inputs are packed into complex words (Q0 with Q1, for example) and input into the second channel. The channel processing the imaginary data is programmed with a phase offset of 90 degrees from the channel processing the real channel (PHASE=0x4000).

In this mode, the chip can support two channels of 3.84 Mbaud UMTS signals.

NOTE: The resampler can not be used in the split IQ mode since it cannot provide data in the two samples per CHREQ format.

#### 3.3.5 Complex Output Mode

The chip may be configured to generate complex rather than real output. In this case the output is the I word followed by the Q word at half the clock rate. The QFLG signal is used to identify the Q half of the output. Complex output applies to all channels on a chip. Likewise, if any chip in a sum path is using complex output, then all chips in the sum path must do so also. The CIC in the complex mode interpolates by N, but only outputs every other sample. This means that the effective CIC interpolation is N/2 in the complex output mode. Note, however, that the CIC gain will still be a function of N, not N/2.

<sup>1.</sup> Hogenhauer, Eugene V., An Economical Class of Digital Filters for Decimation and Interpolation, IEEE transactions on Acoustics, Speech and Signal Processing, April 1981.

<sup>2.</sup> The auto flush mode is a patented feature of the chip. Use of the auto flush mode is highly recommended. CIC instability in cellular basestation chips without the auto flush feature can cause full power white noise to be transmitted on ALL frequencies, interfering with cell users in all nearby cells.

# 3.3.6 The Numerically Controlled Oscillator (NCO)

The tuning frequency of each down converter is specified as a 32 bit word and the phase offset is specified as a 16 bit word. The NCOs can be synchronized with NCOs on other chips. This allows multiple down converter outputs to be coherently combined, each with a unique phase and amplitude. A block diagram of the NCO circuit is shown in Figure 8.

The tuning frequency is set to FREQ according to the formula FREQ =  $2^{32}$ F/F<sub>CK</sub>, where F is the desired tuning frequency and F<sub>CK</sub> is the chip's clock rate. The 16 bit phase offset setting is PHASE =  $2^{16}$ P/2 $\pi$ , where P is the desired phase in radians ranging between 0 and  $2\pi$ . Note that a positive tuning frequency should be used to upconvert the

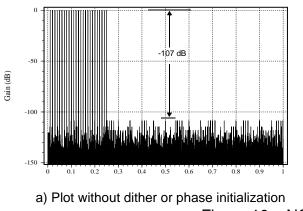

a) Worst case spectrum without dither

signal. A negative tuning frequency can be used to spectrally flip the spectrum of the desired signal. FREQ and PHASE are set in addresses 16 through 31 of the frequency and phase pages.

Note: The frequency word (FREQ) must be doubled in the complex output mode (COMPLX\_OUT=1 in address 13).

The NCO's frequency, phase and accumulator can be initialized and synchronized with other channels using the FREQ\_SYNC, PHASE\_SYNC, and NCO\_SYNC controls in addresses 8 through 11. The FREQ\_SYNC and PHASE\_SYNC controls determine when new frequency and phase settings become active. Normally these are set to "always" so that they take effect immediately, but can be used to synchronize frequency hopping or beam forming systems. The NCO\_SYNC control is usually set to never, but can be used to synchronize the LOs of multiple channels.

Figure 9. Example NCO Spurs

se initialization b) Plot with dither and phase initialization Figure 10. NCO Peak Spur Plot

The NCO's spur level is reduced to below -113 dB through the use of phase dithering. The spectrums in Figure 9 show the NCO spurs for a worst case tuning frequency before and after dithering has been turned on. Notice that the spur level decreases from -105 dB to -116 dB. Dithering is turned on or off using the DITHER\_SYNC controls in addresses 8 through 11.

The worst case NCO spurs at -113 to -116dB, such as the one shown in Figure 9(b), are due to a few frequencies that are related to the sampling frequency by multiples of  $F_{CK}$ /96 and  $F_{CK}$ /124. In these cases the rounding errors in the sine/cosine lookup table repeat in a regular fashion, thereby concentrating the error power into a single frequency, rather than spreading it across the spectrum. These worst case spurs can be eliminated by selecting an initial phase that minimizes the errors or by changing the tuning frequency by a small amount (50 Hz). Setting the initial phase to 4 for multiples of  $F_{CK}$ /96 or  $F_{CK}$ /124 (and to 0 for other frequencies) will result in spurs below -115 for all frequencies.

Figure 10 shows the maximum spur levels as the tuning frequency is scanned over a portion of the frequency range with the peak hold function of the spectrum analyzer turned on. Notice that the peak spur level is -107 dB before dithering and is -121 dB after dithering has been turned on and the phase initialization described above has been used.

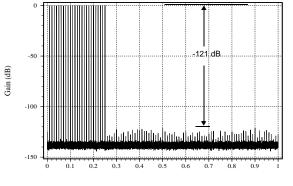

# 3.4 THE OVERALL INTERPOLATION FILTER RESPONSE

The image rejection of the up-convert channel is equal to the stop band rejection of the overall interpolation filter response. The overall response is obtained by convolving the interpolated responses of the PFIR and CFIR filters and CIC filter response. The overall response and appropriate transmit masks are shown in Figure 11 for four common standards. Figure 11a shows the overall response for IS136 (also referred to as DAMPS). Figure 11b shows the response for GSM (input at 2 samples per bit). Figures 11c & d shows the response for IS95 and 3.84 MB UMTS.

# Figure 11. Overall Filter Response

© 2002 Texas Instruments Incorporated

This document contains information which may be changed at any time without notice

# 3.5 THE SUM TREE

As shown in Figure 1, the mixer outputs are rounded to 20 bits and put into the LSBs of a 23 bit sum tree. The sum tree adds all four up-convert channels together. The 23 bit sum tree output is shifted down by three bits and rounded to 19 bits before being added into the LSBs of the external 22 bit sum input. The final 23 bit sum is either saturated to 22 bits (the MSB is checked for overflow) and output from the chip as 22 bits, or is scaled up by 0 to 7bits, rounded into the 8, 10, 12, 14, 16, 18, 20, or 22 MSBs and then output from the chip.

The sum tree gain is equal to 2<sup>SUM\_SCALE-6</sup>, where SUM\_SCALE is 0 to 7 (See address 19 of the IO control page). Overflows in the sum tree are saturated to plus or minus full scale.

The latency from SUMI[0:21] to SUMO[0:21] is eight clock cycles.

# 3.6 OVERALL GAIN

The overall gain of the chip is a function of the input gain setting (G), the sum of the programmable filter coefficients (PFIR\_SUM described in Section 3.3.1), the amount of interpolation in the CIC filters (N described in Section 3.3.3), the scale circuit settings in the CIC filter (SCALE and BIG\_SHIFT described in Section 3.3.3), and the sum tree scale factor (SUM\_SCALE described in Section 3.5). The overall gain, excluding any resampler gain, iS:  $IN = \{\frac{G}{128}\} \{\frac{PTR_SUM}{6536}\} \{N^4 2^{-SCALE + 12 \times BIG_SHIFT + 3}\} \{2^{SUM_SCALE \cdot 6}\}$

where G and PFIR\_SUM can be different for each channel, but N, SCALE, BIG\_SHIFT, and SUM\_SCALE are common to all channels. The resamplers gain, which precedes the input gain, is discussed in Section 3.7.6.

The optimal gain setting is one which will keep the amplitude of the data within the channel as high as possible without causing overflow. For random amplitude data the recommended gain target is to keep the root-mean-squared amplitude of the data close to one-fifth (0.2) full scale (a 14 dB crest factor). This level should be maintained throughout the channel computations. This means that the products

$\left\{ \frac{\text{RMS}}{32768} \right\} \left\{ \frac{\text{G}}{128} \right\} \left\{ \frac{\text{PFIR}_{SUM}}{65536} \right\}$

#### and

# $\left\{ \frac{RMS}{32768} \right\} \left\{ \frac{G}{128} \right\} \left\{ \frac{PFIR\_SUM}{65536} \right\} \left\{ N^4 2^{-(SCALE + 12 \times BIG\_SHIFT + 3)} \right\}$

should both be less than or equal to 0.2, where "RMS" is the root-mean-squared level of the input data. Other crest factors can be used depending upon the application. For example, a

crest factor of 12 dB is adequate if the final number of bits going to a DAC is 12 bits. In most cases the input data will already have the correct crest factor for the application, in

which case the ratio  $\left\{ \frac{\text{RMS}}{32768} \right\}$  will be equal to the crest factor

(e.g., 0.2) and the gain settings in the channel should be set to unity.

In some applications the input amplitude is far from random. For example, QPSK data has constant amplitude. In such cases the largest gain that guarantees no overflow can be calculated from the PFIR coefficients and normally allows a substantially higher gain than the optimal gain for random data of similar power.

Note that the resampler's gain can be used to increase or decrease the RMS input level to the channels.

The sum tree adds the four channels within a single GC4116 together and then adds in sums from other chips using the sum I/O ports. The 22 bit sum I/O path guarantees that no overflow will occur for systems with 8 chips (32 channels) or less. The final chip in the chain should then shift and round the result to optimize the performance of the D/A. Since this represents the sum of many channels the gain should be set with a 14 dB crest factor.

The 14 dB crest factor assumes that the channels can be treated as uncorrelated signals which will result in a random, uniform amplitude distribution. If *M* signals are correlated, however, the amplitude gain can be *M* and the sum tree gain should be set to  $\frac{1}{M}$ . Examples of correlated signals are pure tones or modem signals that have been synchronized so that they might peak at the same time. These signals, however, require a much smaller crest factor, such as 3 dB for pure tones and 6 dB for modem signals. In this case the crest factor of 14 dB will absorb much of the difference in gain between  $\sqrt{M}$  and *M*.

If overflow does occur, then the samples are saturated to plus or minus full scale. Overflow can be monitored using the status register (address 14).

The values of N and BIG\_SHIFT must also satisfy  $2^{(12*BIG\_SHIFT+18)} \ge N^4$  (see Section 3.3.3 for details). If N and BIG\_SHIFT do not satisfy this relationship, then an overflow may occur which may not be detected.

If the auto flush mode is used, then the gain in the CIC must be less than or equal to unity. This means that the values of N, SCALE and BIG\_SHIFT must satisfy  $2^{(SCALE+12*BIG\_SHIFT+3)} \ge N^4$  (see Section 3.3.3 for details).

If attenuation is necessary, for example when multiple channel outputs are to be added together, then the attenuation should be added as close to the output of the chip as is possible - preferably only at the end of the sumtree just prior to going to the D/A.

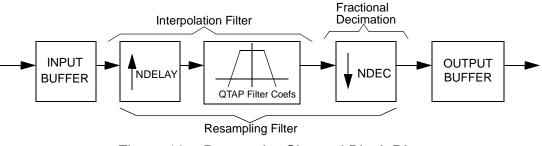

# 3.7 FOUR CHANNEL RESAMPLER

The GC4116 contains a resampler which can be used to feed the up-converter channels in the chip, or can be used as a general resampling resource for a signal processing system. The resampler shares the clock to the chip, but its input, output and control circuitry are independent from the rest of the chip. The resampler in the GC4116 chip is very similar to the one in the GC4016 chip.

The resampler requires the use of the Serial Controller block described in Section 8.

Note that the resampler only works on complex data so the up converter's real or split IQ modes, which require two real samples per complex word, can not use the resampler. Also, the maximum output sample rate from the resampler is CK/44 when it is connected to the GC4116's upconvert channels. This means the upconvert channels must interpolate by at least a factor of 44 (N>=11) when using the resampler.

#### 3.7.1 Resampler Input Format

The resampler inputs are complex samples, 16 bits per I or Q word. The samples are input to the resampler through bit-serial input ports, or through memory mapped registers. A resampler data request signal (RREQ) is output from the chip to identify when the resampler is ready for another complex input sample. The request (RREQ) signal may not be periodic, depending upon the resampling ratio being used.

The bit serial interface to the resampler functions the same as the serial interface to the channels (see Section 2) except the resampler does not support real input mode and the maximum input complex word rate is CK/34.

The Serial Controller is used to tell the resampler input buffer when the next set of serial samples is ready. The Serial Controller can also be used to generate the serial clock and frame strobes for the resampler's input ports (see Section 3.8).

#### 3.7.2 Functional Description

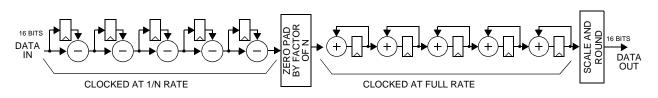

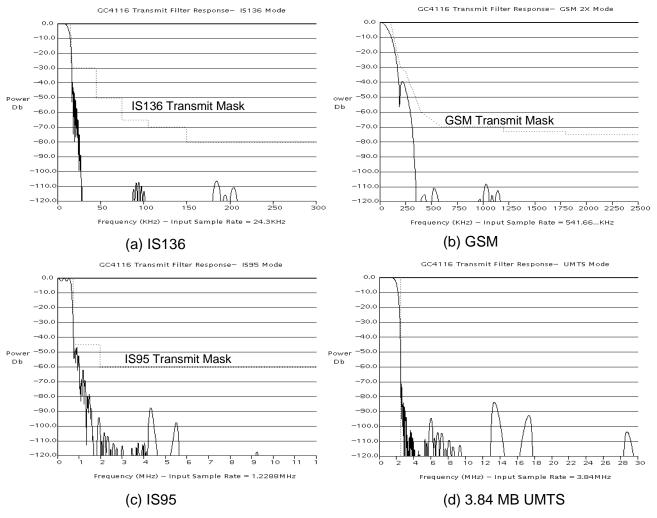

The resampler consists of an input buffer, an interpolation filter, and an output buffer. A functional block diagram of the resampler is shown in Figure 12.

The resampler's sampling rate change is the ratio NDELAY/NDEC where NDELAY and NDEC are the interpolation and decimation factors shown in Figure 12. The decimation amount NDEC is a mixed integer/fractional number. When NDEC is an integer, then the exact sampling instance is computed and there is no phase jitter. If NDEC is fractional, then the desired sampling instance will not be one of the possible NDELAY interpolated values. Instead the nearest interpolated sample is used. This introduces a timing error (jitter) of no more than 1/(2\*NDELAY) times the input sample period.

The input buffer accepts 16 bit data from the serial input ports or the memory mapped input registers. The input buffer serves both as a FIFO between the input and the resampler, and as a data delay line for the interpolation filter. The 64 complex word input buffer can be configured as four segments of 16 complex words each to support 4 resampler channels, or as two segments of 32 complex words each to support 2 resampler channels, or as a single segment of 64 complex words to support a single resampler channel. The number of segments is set by NCHAN in address 16 of the resampler control page.

The interpolation filter zero pads the input data by a factor of NDELAY and then filters the zero padded data using a QTAP length filter. The output of the QTAP filter is then decimated by a factor of NDEC.

The resampling ratio for each channel is determined by setting the 32 bit RATIO control in addresses 16 through 31

Figure 12. Resampler Channel Block Diagram

© 2002 Texas Instruments Incorporated

- 11 -

This document contains information which may be changed at any time without notice

of the resampler ratio page. The value of RATIO is defined as: RATIO =  $2^{26} \left( \frac{\text{NDEC}}{\text{NDELAY}} \right) = 2^{26} \left( \frac{\text{INPUT SAMPLE RATE}}{\text{OUTPUT SAMPLE RATE}} \right)$

Up to four ratios can be stored within the chip. A ratio map register (address 23) selects which ratio is used by each channel.

The three spectral plots shown in Figure 13 illustrate the steps required to resample the channel data. The first spectral plot shows the data just after zero padding. The sample rate after zero padding is NDELAY\*F<sub>S</sub>, where  $F_S$  is the sample rate into the resampler. The second spectrum shows the shape of the QTAP filter which must be applied to the zero padded data in order to suppress the interpolation images. The last spectrum shows the final result after decimating by NDEC.

#### 3.7.3 The Resampler Filter

Figure 13(b) illustrates the spectral shape requirements of the QTAP filter. If the desired signal bandwidth is B, then the filter's passband must be flat out to B/2 and the filter's stop band must start before  $F_S$ -B/2. The user designs this filter assuming a sample rate equal to NDELAY\* $F_S$ . Section 7.6 contains example resampler filters coefficient sets. Other passband and stopband responses can be used, such as

root raised cosine receive filters, as desired. The resampler filter can also be used to augment the CIC, CFIR and PFIR filters' spectral response.

The number of filter coefficients, QTAP, is equal to NMULT\*NDELAY, where NMULT is the number of multiplies available to compute each resampler output, and NDELAY is either 4, 8, 16, 32 or 64 as will be described later. The maximum filter length is 512. The user specifies NMULT in address 17 of the resampler control page.

The filter can be symmetric, or non-symmetric, as selected by the NO\_SYM\_RES control in address 17 of the resampler control page. The symmetric filter is of even length which means the center tap repeats.

The 12 bit filter coefficients are stored in a 256 word memory which can be divided into one, two, or four equal blocks. This allows the user to store one symmetric filter of up to 512 taps, two symmetric filters of up to 256 taps each, or four symmetric filters of up to 128 taps each. The number of filters is set by NFILTER in address 16 of the resampler control page. The filter used by each channel is selected using the FILTER\_SEL controls in address 18 of the resampler control page. The filter lengths are cut in half if the filters are not symmetric. The coefficients are stored in memory with  $h_0$  stored in the lowest address, where  $h_0$  is the

© 2002 Texas Instruments Incorporated - 12 -

This document contains information which may be changed at any time without notice

coefficient multiplied by the newest piece of data. The center tap of a symmetric filter is  $h_{(QTAP/2)-1}$ . The coefficients for multiple filters (NFILTER>1), are interleaved in the 256 word memory.

#### 3.7.4 Restrictions on NMULT

The user does not directly set the value of NDELAY. The chip sets the value of NDELAY using NO\_SYM\_RES, NMULT and NFILTER according to:

NDELAY =

$$Floor_2[256\frac{(2 - NO_SYM_RES)}{(NMULT)(NFILTER)}]$$

where the function FLOOR\_2[X] means the power of two value that is equal to or less than "X". Since NMULT is restricted to be greater than or equal to 6 and less than or equal to 64, then NDELAY is either 4, 8, 16, 32 or 64. The length of the filter is then:

QTAP = (NDELAY)(NMULT)

The value of NMULT determines both the length of the filter and the number of delays in the resampling operation. In general one would choose the largest value of NMULT which gives an adequately large value of NDELAY. The choice of NMULT, however, must meet several restrictions. NMULT must be greater than a minimum, it cannot exceed the available number of multiplier cycles, and it must be less than the input delay line segment size. These restrictions are described below.

The minimum value of NMULT is determined by the minimum number of clock cycles required to update the resampler's state. This is a hardware restriction imposed by the chip's architecture. This limitation is:

$NMULT \ge 6$  if there are two or more channels  $NMULT \ge 7$  if there is only one channel (NCHAN=0)

The maximum value of NMULT must be less than, or equal to, twice the number of clock cycles available to calculate a resampler output. NMULT is the number of multiplier cycles used by the resampler to calculate each output. Since the resampler can perform two multiplies every clock cycle, the value of NMULT cannot exceed two times the number of clock cycles available to the resampler for each channel. The number of clock cycles available to the resampler is equal to the clock rate to the chip divided by the sum of the output sample rates for each resampler channel. Note that the resampler's output sample rate is usually much less than the clock rate, so that NMULT is rarely limited by this restriction.

The value of NMULT must also be less than the size of the delay line formed by the input buffer. The size of the delay

line is either 16 for four resampler channels, 32 for two channels or 64 for a single channel as set by the NCHAN control in address 16 of the resampler control page. This limits NMULT to be less than or equal to 15, 31 or 63 dependent upon the number of resampler channels<sup>1</sup>.

The typical resampler configuration will have four active channels, all using the same filter and the same resampling ratio. The typical configuration has NCHAN set to 4, NFILTER set to 1, NMULT set to 15 and NO\_SYM\_RES set to 0. This sets NDELAY to 32 and QTAPS to 480.

# 3.7.5 Resampler Shift and Round

The gain of each resampler output is adjusted by an up-shift by 0-15 bits (FINAL\_SHIFT). This up-shift is applied just before rounding to 12, 16, 20 or 24 bits (ROUND). The values of FINAL\_SHIFT and ROUND are set in control register 19 of the resampler control page. The resampler gain is:

$RES\_GAIN = (\frac{RES\_SUM}{32768 \times NDELAY})(2^{FINAL\_SHIFT})$

where RES\_SUM is the sum of the QTAP coefficients.

# 3.7.6 By-Passing the Resampler

The resampler is bypassed by using a configuration which has  $h_0$  set to 1024, all other taps set to zero, NMULT set to 7, NO\_SYM\_RES set to 1, FINAL\_SHIFT set to 5, and RATIO set to  $2^{26}$  (0x04000000). Note that the NDELAY term in the RES\_GAIN equation shown above does not apply in this case and should be set to unity in the gain equation.

# 3.7.7 Resampler Output Buffer

The resampler output buffer stores resampler outputs until they are needed. The output is double buffered so that samples from each channel can be stored while previous samples are being output. Resampler output samples are held in the buffer until the RSTART signal is received. When RSTART is received, the buffered data is transferred to the serial output ports which begin to output the samples as serial data streams. The RSTART pulse can only be one CK pulse wide.

The resampler serial output format is shown in Figure 14. The serial frame sync (ROFS) and serial data (ROUT) change on the rising edge of the serial clock (ROCK). The resampler serial outputs can be connected directly to the

<sup>1.</sup> NOTE: If the resampler is being used at much less than its maximum capacity, i.e., NMULT is much less than twice the number of clock cycles available, AND the channels are synchronous, then NMULT may equal the size of the delay line.

<sup>© 2002</sup> Texas Instruments Incorporated

#### Figure 14. Resampler Serial Output

upconverter channel serial inputs if the polarity of the resampler serial clock is inverted by setting RES\_CK\_POL in address 18 of the resampler control page.

#### 3.7.8 Resampler I/O Control

The Resampler will stop if the output buffer is full, or if the input buffer needs more samples. Typically the output rate is constant, such as when the resampler is feeding upconverter channels. The input rate is typically erratic, depending upon when the resampler needs more input data.

The resampler start control (RSTART) is used to start the serial outputs. The RSTART control transfers data from the output buffer into the serial output registers. The serial output frame will then start on the next rising edge of ROCK<sup>1</sup>. If the output buffer is full, then the resampler will stop until the next RSTART pulse has been received.

The resampler input data timing is controlled by the RREQ strobe and the Serial Controller described in the next Section. The RREQ strobe is output when the resampler needs more input data. The RREQ strobe should be connected to the SCSTART input of the Serial Controller. The Serial Controller is then programmed to tell the resampler that the serial transfer is done and new input data is ready. The frame length programmed into the Serial Controller tells the resampler that the new data samples are ready SC\_FRAME\_CNT+18 serial clocks after RREQ. SC\_FRAME\_CNT is set in address 21 of the IO control page. Note that the serial controller can be used to slow down the RREQ rate by setting the minimum period between RREQ strobes to be SC\_FRAME\_CNT+18 serial clocks.

# 1. Actually, the serial frame starts on the next rising edge of ROCK which is 2 CK pulses after RSTART.

© 2002 Texas Instruments Incorporated

# 3.8 SERIAL CONTROLLER

The Serial Controller block can be used to generate the necessary serial clock and frame strobes for the channel or resampler input ports. This frees the input data source (ASIC, FPGA or DSP chip) from having to generate these signals. In the case of a DSP chip, this may allow the input samples to be transferred in a background "DMA" mode that doesn't interrupt the DSP before or after each serial transfer.

The Serial controller generates a serial clock and four serial frame strobes, one for each input serial port. Each frame strobe can be programmed to be delayed by a different amount from the Serial Controller start (SCSTART) pulse.

The serial controller contains a serial clock generator and a frame counter. The serial clock (SCCK) is generated by dividing down CK by 1 to 16 (see SC\_CK\_DIV in address 20 of the IO control page). The serial clocks in multiple chips can be synchronized by using the SIA or SIB sync inputs, as selected by the SCCK\_SYNC control bits in address 20 of the IO control page. Two copies of the serial clock are output on pins SCCK0 and SCCK1. Two copies are output to increase the fanout of the clock.

The start signal (SCSTART) is clocked into the chip on the rising edge of CK. SCSTART is expected to be one CK clock cycle wide. Typically SCSTART is either connected to CHREQ or RREQ, depending upon whether the it is being used for the up convert channels or the resampler.

The 8 bit frame counter is started by SCSTART at the value SC\_FRAME\_CNT. The counter is decremented at the serial clock rate until it reaches zero. The counter will continue to decrement for 18 more serial clocks if it is being used with the resampler (SC\_MODE=0 in address 17 of the IO Control page), at which time it will tell the resampler that the serial frame is done and a new resampler computation can begin. The counter will count down 2 more serial clocks and stop if the serial controller is being used with the channels (SC\_MODE=1).

The serial frame strobes SCFSA, SCFSB, SCFSC and SCFSD are generated by comparing the upper four bits of the frame counter to SC\_FS\_DELAY\_A, SC\_FS\_DELAY\_B, SC\_FS\_DELAY\_C and SC\_FS\_DELAY\_D. A frame strobe is output when the delay values match the counter and the lower four bits of the counter are zero. This allows the frame strobes to be generated on 16 serial clock boundaries.

NOTE: If the 4 LSBs of SC\_FRAME\_CNT are zero, and one of the SC\_FS\_DELAY values match the upper 4 bits of SC\_FRAME\_CNT, then that frame strobe will be active when the serial controller is idle and waiting for another SCSTART pulse. In general, the lower 4 bits of SC\_FRAME\_CNT should be non-zero.

The serial control supports both the packed and unpacked serial modes, where the unpacked mode expects a serial frame strobe for each 16 bit word of a complex pair, and the packed mode expects a single frame strobe for the 32 bit complex pair.

The frame strobe in the packed mode (PACKED=1 and SC\_MODE=1, or RES\_PACKED=1 and SC\_MODE=0, in addresses 16 and 17 of the IO Control page) may be positioned in one of 15 delays, corresponding to SC\_FS\_DELAY values of 0 through 14. In the unpacked mode only the upper three bits of the counter are compared with the upper 3 bits of the SC\_FS\_DELAY values. The lower bit of the SC\_FS\_DELAY values must be zero. This means that the values will match twice, outputting two frame strobes, 16 bits apart.

If the input data is coming from four serial streams, so that the four frame strobes should be sent at the same time, then SC\_FRAME\_CNT should be set to 17, and the four SC\_FS\_DELAY values should be set to "1". Larger values of SC\_FRAME\_CNT can be used in this case in order to spread out the RREQ periods.

If the data is coming from a single TDM bus, then SCFSA (or SCSTART) can be sent to the data source to start the TDM frame, and then SCFSB, SCFSC and SCFSD can be delayed to identify the appropriate time slots in the TDM bus.

When the serial controller is being used with the channel inputs (not the resampler) and the upconvert interpolation factor is 32 or 36, then the frame delays must be used to delay the serial frames to start between 3 to 9 clocks (CK) before the next CHREQ strobe. This is because of the requirement that the serial transfer of 32 bits is completed 3 to 9 clocks before the next CHREQ strobe (See Section 3.2.1). This means that for an interpolation of 32 (the CIC interpolation factor N is 8), SC\_FRAME\_CNT should be set to 23 and the SC\_FS\_DELAY values should be "0". For an interpolation of 36 (N=9) SC\_FRAME\_CNT should be 27. For larger interpolation factors the default value of 17 can be used. NOTE that if the serial clock is divided, then similar delay values may need to be used in order to insure that the serial frame is complete before the next CHREQ.

In the wideband (splitIQ) mode (see Section 3.3.4) the channel serial inputs will want two samples, 16 bits each, after each channel request. The serial control can generate two frame strobes for each CHREQ, by using the unpacked mode (PACKED=0). In this mode the circuitry which

generates the GC4116 input data doesn't need to pack two samples into a 32 bit word, instead it sends a 16 bit word every time it receives the

# 3.9 CLOCKING

The chip clock rate is equal to the output data rate which can be up to 106 MHz. An internal clock doubler doubles the clock rate so that the internal circuitry is clocked at twice the data rate. The clock doubler requires 4-5 clocks to adapt to the rate of the incoming clock during which time the reset should be active. A gated clock, not uniform clock period clock, is not suitable for this device above 40 MHz. A test mode (ext\_2xck) allows the use of an external double rate clock (ck2x pin). This is intended for use in production test. Please contact Texas Instruments if further information on this mode is needed.

#### 3.10 POWER DOWN MODES

The chip has a power down and clock loss detect circuit. This circuit detects if the clock is absent long enough to cause dynamic storage nodes to lose state. If clock loss is detected, an internal reset state is entered to force the dynamic nodes to become static. The control registers are not reset and will retain their values, but any data values within the chip will be lost. When the clock returns to normal the chip will automatically return to normal. In the reset state the chip consumes only a small amount of standby power. The user can select whether this circuit is in the automatic clock-loss detect mode, is always on (power down mode), or is disabled (the clock reset never kicks in) using the DISABLE\_CK\_LOSS control bit in address 13 and the GLOBAL\_RESET control bit in address 5. The whole chip, or individual down converter channels can be powered down. Individual channels are powered down using the RESET\_A, B. C and D control bits in address 5.

#### 3.11 SYNCHRONIZATION

Each GC4116 chip can be synchronized through the use of one of two sync input signals, an internal one shot sync generator, or a sync counter. The sync to each circuit can also be set to be always on or always off. Each circuit within the chip, such as the sine/cosine generators or the interpolation control counter can be synchronized to one of these sources. These syncs can also be output from the chip so that multiple chips can be synchronized to the syncs coming from a designated "master" GC4116 chip. The 2 bit sync mode control for each sync circuit is defined in Table 1:

| Table | 1: | Sync | Modes |

|-------|----|------|-------|

|-------|----|------|-------|

| MODE | SYNC SOURCE                                                                                    |

|------|------------------------------------------------------------------------------------------------|

| 0    | off (never asserted)                                                                           |

| 1    | SIA or SIB (See Table 2)                                                                       |

| 2    | TC (terminal count of the sync counter)<br>or ONE_SHOT (if USE_ONESHOT in<br>address 0 is set) |

| 3    | on (always active)                                                                             |

NOTE: the internal syncs are active high. The SIA and SIB inputs have been inverted to be the active high syncs SIA and SIB in Table1.

The ONE\_SHOT sync (address 0, bit 7) can either be a level or a pulse as selected by the OS\_MODE control bit in address 13. The level mode is used to initialize the chip, the pulse mode is used to synchronously switch frequency, phase or gain values.

The SIA and SIB external sync inputs are provided to allow independent synchronization of different features of the GC4116 chip. Sync mode 1 is either SIA or SIB, depending upon what circuit is being synchronized by the sync circuit. Table 2 lists all of the sync circuits, what they do, which sync mode 1 it uses, and the suggested default mode settings.

The SIA sync is intended to be used during initialization only. The circuits connected to SIA are ones that should be initialized once, and then let free run. SIB is intended to be used for those circuits which may be periodically initialized, such as changing frequency, phase and gain between TDMA bursts.

The interpolation control counter generates the request strobe (CHREQ) output from the chip. This counter can be syncronized using the input SIA sync (INT\_SYNC=1). This allows the user to lock the timing of the request strobe to the SIA timing. If this is done, and BIG\_SHIFT is even, then the CHREQ strobe will go high 9 clock cycles after the SIA strobe. For example, if the SIA signal is active during clock cycle 0, then CHREQ will go high during clock cycle 9 and then repeat every 4N clocks (or 2N clocks in the real input mode) thereafter. If BIG\_SHIFT is odd then the delay is 8 clock cycles.

#### Table 2: Sync Descriptions

| Sync Circuit         | Mode 1 | Description                                                                                                                                  | Default |

|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|---------|

| INT_SYNC             | SIA    | Interpolation control counter.<br>Sets timing of CHREQ.                                                                                      | 1(SIA)  |

| COUNTER_<br>SYNC     | SIA    | Internal sync counter.<br>Generates TC sync. Mode 2<br>is always ONE_SHOT                                                                    | 2 (OS)  |

| OUTPUT_<br>SYNC      | SIA    | The output sync (SO) selection.                                                                                                              | 2 (TC)  |

| GAIN_SYNC            | SIB    | A single bit sync selection.<br>GAIN_SYNC=0 means the<br>gain is applied immediately.<br>GAIN_SYNC=1 means the<br>gain is applied after SIB. | 0       |

| DIAG_SYNC            | SIA    | Selects when to start the diagnostic ramp and to store the diagnostic checksum.                                                              | 2 (TC)  |

| FREQ_SYNC            | SIB    | Selects when new frequency settings take effect.                                                                                             | 3 (on)  |

| PHASE_SYNC           | SIB    | Selects when new phase settings take effect.                                                                                                 | 3 (on)  |

| NCO_SYNC             | SIB    | Reset the NCO phase accumulator                                                                                                              | 0 (off) |

| DITHER_<br>SYNC      | SIB    | Clears the NCO dither circuit.                                                                                                               | 0 (off) |

| FLUSH _<br>(A,B,C,D) | SIA    | Starts a flush of the channel                                                                                                                | 1 (SIA) |

| ROCK_SYNC            | SIA    | Syncs the resampler's serial output clock. Mode 2 is SIB.                                                                                    | 1 (SIA) |

| SCCK_SYNC            | SIA    | Syncs the serial controller's serial output clock. Mode 2 is SIB.                                                                            | 1 (SIA) |

| RES_SYNC             | Note 1 | Syncs the resampler during initialization                                                                                                    | 2 (SIA) |

| RATIO_SYNC           | Note 1 | Selects when a new resampler ratio takes effect.                                                                                             | 3 (SIB) |

#### 3.12 INITIALIZATION

ONE\_SHOT, and modes 6 and 7 are "on".

Two initialization procedures are recommended. The first is recommended for multi-GC4116 chip configuration. The second can be used for stand alone GC4116 chips.

#### 3.12.1 Initializing Multiple GC4116 Chips

The multi-GC4116 initialization procedure assumes that the  $\overline{SIA}$  sync input pins of all GC4116 chips are tied together and are connected to the  $\overline{SO}$  output of the "master" chip, or to a common sync source. The procedure is to:

(1) reset the chip by setting address 5, the reset register, to 0xFF;

(2) configure the rest of the chip including setting the INT\_SYNC, RES\_SYNC and FLUSH\_(A,B,C,D) to be  $\overline{SIA}$ , the OS\_MODE to be 1, and the OUTPUT\_SYNC to be OS (see Table 1);

(3) assert the  $\overline{SIA}$  sync input by setting the ONE\_SHOT control bit high (or by setting the external  $\overline{SIA}$  source low);

(4) release the global resets by setting address 5 to 0x00; and

(5) release the SIA sync by setting ONE\_SHOT to 0 (or the external SIA source high).

The global resets are asserted before configuring the chip so that the operation of all of the pins, including the directions of the bidirectional and tristate pins, will be established before the global resets release them. The SIA sync is asserted before releasing the global resets so that the channels will remain in a reset state after the global resets are released. All channels and the resampler will then start synchronously by releasing the SIA sync. If there are multiple chips which need synchronized, then synchronously releasing the SIA sync to them all will force them all to be synchronized.

The frequency, phase and gain of multiple chips can be initialized by holding  $\overline{\text{SIB}}$  low and then releasing it to all of the chips at the same time.

#### 3.12.2 Initializing Stand Alone GC4116 chips

The initialization sequence for a stand alone GC4116 chip is similar to the one for the multi-GC4116 procedure, except that the ONE\_SHOT is used to synchronize the chip, not the  $\overline{SIA}$  input sync. The procedure is to:

(1) reset the chip by setting address 5, the reset register, to 0xFF;

(2) configure the rest of the chip including setting the INT\_SYNC, RES\_SYNC and FLUSH\_(A,B,C,D) to be ONE\_SHOT (mode 2) and the OS\_MODE to be 1;

(3) assert the syncs by setting ONE\_SHOT high;

(4) release the global resets by setting address 5 to 0x00; and

(5) release the syncs by setting ONE\_SHOT to 0.

# 3.13 DATA LATENCY

The data latency through the chip is defined as the delay from the rising edge of a step function input to the chip to the rising edge of the step function as it leaves the chip. This delay is dominated by the number of taps in each of the filters. An estimate of the overall latency through the chip, expressed as the number of CK clock cycles is:

(CIC latency = 2.5N) + (CFIR latency = 16N) +

(PFIR latency = N\*PTAP) + (Resampler latency) + (Input delay) + (Pipeline delay)

where N is the CIC interpolation ratio and PTAP is the number of PFIR taps. PTAP is normally 63. Latency can be reduced by using the NO\_SYM\_PFIR mode to shorten the filter.

The Resampler latency, if the resampler is being used, is approximately 2N\*NMULT plus a resampler input sample period and a resampler output period to allow for resampler I/O buffering. The latency in the resampler can be minimized by using the bypass configuration (See Section 3.7.7).

The Input delay is approximately two input sample periods due to the double buffering in the serial input ports. The Pipeline delay is approximately 40 clock cycles.

#### 3.14 DIAGNOSTICS

The chip has an internal ramp generator which can be used in place of the data inputs for diagnostics. An internal checksum circuit generates a checksum of the output data to verify the chip's operation. See Section 7.12 for diagnostic configurations and checksums.

Besides the internal diagnostics, the chip supports initial board debug through special input and output tests. The suggested procedure for bringing up the GC4116 chip on a board is to first check the control interface by writing to the control registers and reading them back. The diagnostics described in Section 7.12 should be run next, followed by the output and input tests described in Sections 7.13 and 7.14. If these pass successfully, then the configuration customized for the desired application should work.

# 3.15 JTAG

The GC4116 supports a four pin (TDI, TDO, TCK and TMS) boundary scan interface. Contact Texas Instruments to receive the GC4116's BSDL file. TDI, TMS and TCK have internal pull resistors to Vpad. Leave open or pulled up if unused.

© 2002 Texas Instruments Incorporated

# 3.16 MASK REVISION REGISTER

An 8 bit mask revision code (REVISION) can be read from address 31 of page 0. The revision code allows users to

determine, through software, what version of the GC4116 chips are being used. The current mask revision codes are:

#### **Table 3: Mask Revisions**

|                             | GC4116       |                         |                                                                           |  |  |  |  |  |  |

|-----------------------------|--------------|-------------------------|---------------------------------------------------------------------------|--|--|--|--|--|--|

| Revision Code<br>(REVISION) | Release Date | Mask Code on<br>Package | Description                                                               |  |  |  |  |  |  |

| 0                           | April 2000   | SAMPLE                  | Early samples                                                             |  |  |  |  |  |  |

| 1                           | Nov. 2000    | 1002ACBA                | First Release, Revision 1                                                 |  |  |  |  |  |  |

| 2                           | March 2001   | 1002ACBB                | Revision 2, adds JTAG, corrects initialization bug                        |  |  |  |  |  |  |

| 2                           | 2001-2002    | 1002ACBC<br>1002ACBD    | Yield enhancements, no functional, timing, electrical or thermal changes. |  |  |  |  |  |  |

#### 4.0 PACKAGING